各 位

会 社 名 株式会社岡本工作機械製作所代表 者 代表取締役社長 石井 常路 (コード番号 6125 東証 スタンダード市場) 間合せ先 取締役常務執行役員 管理本部長 高橋 正弥 (TEL, 027—385—5800)

# 「研究成果最適展開支援プログラム」開発成功のお知らせ

当社半導体関連装置開発部門において、実用化を目指して研究開発を進めておりました「Si 貫通電極ウェーハ全自動研削装置」の計画につきまして、国立研究開発法人科学技術振興機構(以下、「JST」といいます)から支援を受ける開発が終了し、開発結果の成功認定を受けましたことをお知らせいたします。

なお、この成功は2016年10月にJSTの研究成果最適展開支援プログラム(A-STEP) NexTEP-A タイプとして開始され、2024年7月にかけて当社にて実用化開発を進めていたものになります。

記

#### 1. 「研究成果最適展開支援プログラム」とは

当該事業は、大学・公的研究機関等で生まれた科学技術に関する研究成果を国民経済上重要な技術として 実用化することで、研究成果の社会還元を目指す技術移転支援プログラムです。

### 2. 研究の概要

添付「シリコンと銅を同時に研削する全自動装置の開発に成功 ~ビアミドルSi 貫通電極を用いた 3次元実装技術の普及を後押し~」をご参照ください。

### 3. 今後の見通し

今期の業績に与える影響はございませんが、今後開示が必要な場合には速やかにお知らせいたします。

以上

令和6年10月29日

科学技術振興機構 (JST) Tel:03-5214-8404 (広報課)

株式会社岡本工作機械製作所 Tel: 027-385-5800(総務部)

シリコンと銅を同時に研削する全自動装置の開発に成功 ~ビアミドルS:貫通電極を用いた3次元実装技術の普及を後押し~

# ポイント

- ▶ 半導体回路の性能向上を図る方法の1つとして、回路を平面ではなく立体に集積する「3次元実装技術」が注目されているが、コストの問題や歩留まり(良品率)の低さが制約となり、一部の高機能デバイスでしか実用化されていなかった。

- ▶ 本開発では、シリコン(Si)ウェーハ裏面からSi貫通電極を露出させる全自動研削装置を開発し、歩留まり低下の要因であるSi貫通電極の長さのばらつきを低減するとともに、Siと金属部の銅(Cu)の安定的な同時研削を実現した。また、ウェーハ上の残留Cu除去にも成功した。

- ▶ 本装置により、Si貫通電極形成プロセスが効率化され、接続電極を用いない直接積層が可能となったことで、さまざまなデバイスへの応用と半導体回路の高性能化が期待される。

JST(理事長 橋本 和仁)は、研究成果最適展開支援プログラム(A-STEP) NexTEP-Aタイプの開発課題「Si貫通電極ウェーハ全自動研削装置」の開発結果を成功と認定しました。この開発課題は、産業技術総合研究所 先端半導体研究センター 渡辺 直也 主任研究員の研究成果を基に、JSTが支援し、平成28年10月から令和6年7月にかけて株式会社岡本工作機械製作所(本社:群馬県安中市、代表者:代表取締役社長 石井 常路)において実用化開発を進めていたものです。

本開発ではSiウェーハの裏面からSi貫通電極<sup>注1)</sup>を露出させるための研削<sup>注2)</sup>加工を可能とする「Si貫通電極ウェーハ全自動研削装置」を開発しました。この装置では、多くの気孔があり目詰まりしにくい研削砥石(といし)、ウェーハの厚み自動補正機能などにより、Si貫通電極の長さのばらつきを極限まで小さくし、SiとCuの安定的かつ精緻な同時研削を実現しました。また、研削加工後のウェーハをアルカリイオン水洗浄、無電解めっきおよびSiウエットエッチング<sup>注3)</sup>により処理することで、Si上の残留Cuを除去することにも成功しました。これにより、Si貫通電極部分からのCuの溶け出しを防止しつつ、Siウェーハ上の残留Cuを、一般的な金属濃度以下まで除去すること

ができました。

本装置によって、S: 貫通電極形成プロセスが効率化されるとともに、ウェーハレベルでの直接積層 (バンプ<sup>注4)</sup> を用いない積層) が可能になり、その結果、S: 貫通電極形成プロセスの低コスト化と歩留まりの向上が実現できると考えられます。今後はデバイスメーカーとの協業を通じて、さまざまなデバイスへの適用と半導体回路の高性能化が期待されます。

本成果は、以下の事業・研究領域・研究課題によって得られました。

事 業 名:研究成果最適展開支援プログラム(AISTEP) NexTEP-Aタ

イプ

開発課題名: Si貫通電極ウェーハ全自動研削装置

開発実施企業:株式会社岡本工作機械製作所

代表研究者:渡辺 直也 産業技術総合研究所 先端半導体研究センター 主任研究員

研究期間:平成28年10月~令和6年7月

上記研究課題では、Si貫通電極ウェーハ全自動研削装置の開発・製品化を目的としてい

ます。

### <開発の背景と経緯>

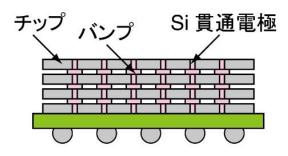

昨今、半導体回路(主にSi製)の微細化について物理的な限界が懸念される中、半導体回路の性能向上の方法の1つとして、回路を平面ではなく立体に集積する「3次元実装技術」が注目されています(図1)。Si貫通電極を用いた方法では、Si貫通電極(金属部材料は主にCu)を形成した半導体回路チップを、バンプと呼ばれる接合用電極を用いて電気的・機械的に接続しながら垂直方向に積層するものです。

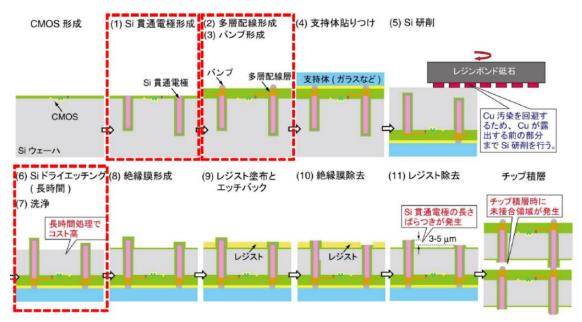

S:貫通電極の形成方法としては、主にビアミドルプロセス<sup>注5)</sup>とビアラストプロセス<sup>注6)</sup>の2つがあります。特にビアミドルプロセス(図2)は、微細なSi貫通電極を形成しやすいという利点がある一方で、ウェーハ(Si)を薄化してSi貫通電極をウェーハ裏面から露出させる際に、脆性(ぜいせい)材料のSiと延性材料のCuを同時研削すると、砥石にCuが目詰まりすることで研削性能の低下を招きます。また、SiウェーハにわずかなCuが付着、残留するため、回路素子の特性変動など品質低下が懸念されます。それらを防止する安定的な同時研削は困難であり、現状では、サポートガラス貼り付け後にSiのみを研削し、長時間のSiドライエッチング注3)でSi貫通電極をSi内部より出現させ、絶縁膜を成膜した後にCMP<sup>注7)</sup>でSi貫通電極を露出させるという、高コストで複雑な工程を余儀なくされています。加えて、Si貫通電極形成時のSiウェーハの深掘りエッチングの際に、Si貫通電極のおのおのの長さにばらつきが生じるため、Si貫通電極が適切に露出されないことが多く、積層の歩留まりが低下します。

現状はコストや歩留まりの低さが制約となり、ビアミドルプロセスによるSi貫通電極形成は積層DRAM<sup>注8)</sup>など一部の高機能なハイエンドデバイスでしか実用化されていません。今後、ビアミドルプロセスを通じた3次元実装をさまざまなデバイスに適用していくためには、これらの問題を解決し、コスト低減と歩留まり向上を行う必要があります。

## <開発内容と成果>

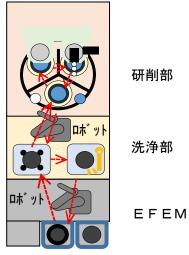

本開発では、Siウェーハ(直径300ミリメートル)の裏面から研削加工でSi貫通電極を露出させ、コスト低減および歩留まり向上を実現するための「Si貫通電極ウェーハ全自動研削装置」(図3)を開発しました。この装置は、脆性材料であるSiと延性材料であるCuの安定的かつ精緻な同時研削技術を開発して搭載することで実現しました。また装置とは別に、Siウェーハ上の残留Cuの除去技術を開発しました。

### SiとCuの安定的かつ精緻な同時研削技術

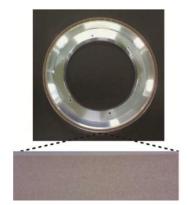

多くの気孔があり目詰まりしにくい研削砥石を開発するとともに、研削時に 砥石に付着した C u を除去し、常に砥石表面を同じ状態に保てるように高圧水 で洗浄する技術を開発しました(図 4)。これにより、研削性能が低下しない安 定した研削を実現しました。 また、従来方法では、加工を一旦途中で止めた後にウェーハの形状を測定し、その測定結果を基に砥石の傾きを補正して再度加工するため、研削時間が多くかかりました。この方法を改め、加工中に厚み測定器(IRセンサー)を使ってリアルタイムに形状を測定しながら研削ヘッド(砥石)の傾きを自動補正するというダイナミックな研削方法を開発しました。その結果、補正を行わない場合と同じ時間でSi貫通電極の長さのばらつきを極限まで小さくし、高いレベルの平坦性を実現しました。

## Siウェーハ上の残留Cuの除去技術

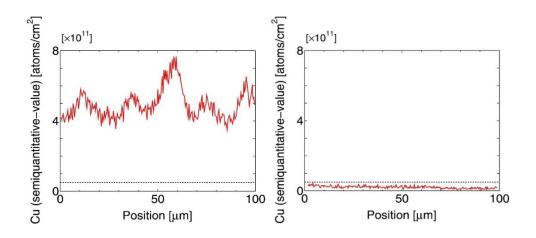

SiとCuの同時研削後に、Si表面にわずかに付着、残留するCuを除去する技術も開発しました。具体的には、SiとCuの同時研削で露出したSi貫通電極のCu面に対して、無電解ニッケルーボロン(Ni-B)めっきで表面保護処理を行った後、Siウエットエッチングで処理しました。これにより、Si貫通電極部分からのCuの溶け出しを防止しつつ、Si上の残留Cuを一般的な金属濃度以下まで除去することができるため、回路素子の特性変動などの品質低下といった懸念を解消できます(図5)。

### く今後の展開>

S: 貫通電極ウェーハ全自動研削装置によって、S: 貫通電極形成でのビアミドルプロセスが効率化されました。バンプを用いない直接積層が可能となったことで(図6)、従来プロセスと比較して大幅な低コスト化かつ高い歩留まりが実現できると考えられます。

今後はデバイスメーカーとの協業を通じて、ハイエンド用だけでなく、現在普及著しいIoT(Internet of Things)用、人工知能用などさまざまなデバイスへの適用と半導体回路の高性能化が期待されます。

# <参考図>

図 1:3 次元実装した回路のイメージ。Si 貫通電極を形成した半導体回路を、 バンプを用いて電気的・機械的に接続しながら、垂直方向に積層している。

### ※赤点線枠内は課題が発生する工程

図2:ビアミドルプロセスにおける課題。ドライエッチングや洗浄など高コストで長時間の工程が必要となる。また、Si貫通電極の長さにばらつきが生じるため、Si貫通電極が適切に露出されないことが多く、積層の歩留まりが低下する。

図3:Si貫通電極ウェーハ用全自動研削装置の外観(左)、レイアウト(右)。 ウェーハ搬送システムである「Equipment Front End Module (EFEM)」と洗浄部ではそれぞれのロボットがウェーハを搬送しステージ間を移動していく。研削部ではインデックステーブルが回転することで粗研削、仕上げ研削へとウェーハが移動する。

図4:通常の砥石(左)と本開発により得られた砥石(右)。左と比べ、右の砥石には多くの気孔があるため目詰まりしにくい構造になっている。

図5:金属汚染量の評価結果。SiとCuの同時研削直後(左)、残留金属低減処理後(右)。無電解Ni-Bめっき後、Siウエットエッチングを行うことでSi上の残留Cuを、一般的な金属濃度以下まで除去することができた。

## ※赤点線内が新たに導入し開発した工程 CMOS 形成 (1) Si 貫通電極形成 (2) 多層配線形成 (3) 支持体貼りつけ ウェーハ厚さ自動補正 Si/Cu 同時研削 新砥石の導入と高圧水洗浄の効果 SiとCuの同時加工を実現。 砥石の傾き調整で、Si貫通電極の 多層配線層 支持体 CMOS 高圧水 ウェ―ハ積層 (6) アルカリエッチング (7) 絶縁膜堆積 (8) CMP (5) 無電解めっき リフトオフ効果で 微量残存 Cu の除去 全面接合で高信 頼性を確保する

図6:本装置で実現した新しいビアミドルプロセス。Si 貫通電極形成でのビアミドルプロセスを効率化するとともに、バンプを用いない直接積層が可能となった。

## <用語解説>

#### 注1) Si貫通電極:

半導体ウェーハ(チップ)の表面から裏面まで貫通して形成された電極。電極の金属部は主に Cu で形成される。

## 注2) 研削:

砥石を回転させながら加工対象(今回の場合は半導体ウェーハ)に押し当てて 削り取り、目的形状に仕上げる加工。砥石は、砥粒と呼ばれる硬い粒をボンド材 で固めたものである。

## 注3) Siウエットエッチング、Siドライエッチング:

Siウエットエッチングは、化学薬品(エッチング液)を使って選択的に溶解し、ウェーハを加工する方法。Siドライエッチングは、高真空プラズマを用いてウェーハを加工する方法。

## 注4) バンプ:

半導体チップを縦方向に積層するための接合用電極。

#### 注5) ビアミドルプロセス:

Si 貫通電極の形成を、トランジスタ形成と多層配線およびバンプ形成の間に行うプロセス。

## 注6) ビアラストプロセス:

S:貫通電極の形成を、多層配線およびバンプ形成の後に行うプロセス。

#### 注7) CMP:

Chemical Mechanical Polishingの略。化学的機械研磨。研磨剤に含まれる成分による化学的な処理と、機械的な研磨を同時に行う。

## 注8) DRAM:

Dynamic Random Access Memoryの略。RAMと呼ばれる半導体メモリーの一種。パソコンのメインメモリーなどに広く使われている。

## くお問い合わせ先>

<開発に関すること>

## 株式会社岡本工作機械製作所

技術開発本部 ナノプロセス技術部 要素プロセス開発課 〒379-0135 群馬県安中市郷原2993 Tel: 027-385-5155 Fax: 027-385-4053

E-mail: tech@okamoto.co.jp

## <JST事業に関すること>

## 下田 修(シモダ オサム)

科学技術振興機構 スタートアップ・技術移転推進部 実装支援グループ

〒102-0076 東京都千代田区五番町7 K's 五番町

Tel: 03-5214-8995 Fax: 03-5214-0017

E-mail: jitsuyoka@jst.go.jp

## <報道担当>

# 科学技術振興機構 広報課

〒102-8666 東京都千代田区四番町5番地3

Tel: 03-5214-8404 Fax: 03-5214-8432

E-mail: jstkoho@jst.go.jp

## 株式会社岡本工作機械製作所 総務部

〒379-0135 群馬県安中市郷原2993

Tel: 027-385-5800 Fax: 027-385-5880

E-mail: pr@okamoto.co.jp